Wayne State University

Wayne State University Dissertations

1-1-2016

# Optimization Of Transition-Metal Dichalcogenides Based Field- Effect- Transistors Via Contact Engineering

Meeghage Madusanka Perera *Wayne State University,*

Follow this and additional works at: http://digitalcommons.wayne.edu/oa\_dissertations Part of the <u>Nanoscience and Nanotechnology Commons</u>, and the <u>Physics Commons</u>

#### **Recommended** Citation

Perera, Meeghage Madusanka, "Optimization Of Transition-Metal Dichalcogenides Based Field- Effect- Transistors Via Contact Engineering" (2016). *Wayne State University Dissertations*. 1657. http://digitalcommons.wayne.edu/oa\_dissertations/1657

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

## OPTIMIZATION OF TRANSITION-METAL DICHALCOGENIDES BASED FIELD-EFFECT-TRANSISTORS VIA CONTACT ENGINEERING

by

## MEEGHAGE MADUSANKA PERERA

## DISSERTATION

Submitted to the Graduate School

of Wayne State University

Detroit, Michigan

in partial fulfillment of requirements

for the degree of

## **DOCTOR OF PHILOSOPHY**

2016

MAJOR: PHYSICS

Approved By:

| Advisor          | Date |

|------------------|------|

| Committee Member | Date |

| Committee Member | Date |

| Committee Member | Date |

## **©COPYRIGHT BY**

### MEEGHAGE MADUSANKA PERERA

2016

All Rights Reserved

## DEDICATION

"To my wife Maheeka, daughter Kiyara, my brother, parents and anyone who loves 2D materials"

#### ACKNOWLEDGMENTS

I would like to extend my deepest gratitude to all the people who helped me to be successful in my PhD journey. A lot of people helped me, motivated me to complete my doctoral work.

First and foremost I would like to thank my PhD research advisor Dr.Zhixian Zhou, for his expertise guidance, unlimited patience, generous help and most importantly his vision that helped me to be highly successful as a PhD candidate. Being a well focused and highly motivated scientists, Dr.Zhou influenced me to be an outstanding researcher and highly productive graduate student. The life lessons I learned by working with him, not only helped me to complete my PhD research work, but also will be helpful me to be successful in my life beyond the graduate school. My sincere thank goes to all the members in my thesis committee Dr.Boris Nadgorny, Dr.Jian Huang and Dr.Mark Ming- Cheng Cheng for their highly valuable advice and help.

I would be grateful for the senior members in Zhou lab for their warm welcome and providing me initial help and training to start my PhD research work. My special thank goes to Dr.Ming-Wei Lin and Mr. Chongyu Wang who introduced necessary techniques and teaching important skills that helped me to be successful in my research work. My special thank goes to my batch mates in Zhou lab, Dr. Hsun Jen Chuang and Mr. Bhim Chamlagain for their support, valuable discussions and making this journey a memorable one.

My special thank goes to my Wife Maheeka, for her unlimited support, patience and motivation that helped me to be successful in my PhD journey. Being a PhD candidate, she had to work intense in her PhD research. However, she managed a great work life balance to help me and the family. I'm so thankful to my little daughter Kiyara , who came to my life during the final stage of my PhD work. I would like to thank my brother and parents, who motivated me whenever I need it even they are not physically close to me.

Finally, I would like to thank all my wonderful friends who continuously helped me and motivated me during last five unforgettable years in my life.

| TABLE OF | CONTENTS |

|----------|----------|

|----------|----------|

| Dedicationii                                                                               |

|--------------------------------------------------------------------------------------------|

| Acknowledgementsiii                                                                        |

| List of Figures viii                                                                       |

| CHAPTER 1:GENERAL INTRODUCTION1                                                            |

| 1.1) Development of 2D materials beyond Graphene1                                          |

| 1.2 Challenges in 2D materials based FETs2                                                 |

| 1.2.a) Understanding the main challenge2                                                   |

| 1.2.b) Contact engineering as a solution                                                   |

| 1.3 Methods to reduce contact resistance                                                   |

| 1.3.1) Metal contacted MoS <sub>2</sub> FETs with Ionic liquid gating4                     |

| 1.3.2) Highly doped graphene as low-resistance contact material for MoS <sub>2</sub> FETs4 |

| 1.3.3) 2D/2D contacts with slightly doped channel                                          |

| CHAPTER 2:EXPERIMENTAL METHODS                                                             |

| 2.1 Cleaning the samples and substrates                                                    |

| 2.2 Sample fabrication with mechanical exfoliation7                                        |

| 2.3 Dry transfer method                                                                    |

| 2.3.1) Preparing PDMS10                                                                    |

| 2.3.2) Preparing for the transfer                                                          |

| 2.3.3) Transferring the samples onto substrate                                             |

| 2.7 Electron beam lithography and metal deposition                                         |

| 2.7.1)The main steps of E-beam lithography process15                                       |

| 2.7.2) Pattern Development                                                                 |

| 2.8) Metal Deposition                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------|

| 2.8.a)Annealing process                                                                                                      |

| 2.9) Doping methods                                                                                                          |

| 2.9.1) Ionic Liquid (IL) doping19                                                                                            |

| 2.9.2) Benzyl Viologen doping method                                                                                         |

| 2.10) The summary of devices types that are fabricated for each project                                                      |

| CHAPTER 3: IMPROVED PERFORMANCE IN FEW LAYER MOS <sub>2</sub> FETS VIA IONIC LIQUID GATING                                   |

| 3.1 Introduction                                                                                                             |

| 3.2 Results and discussion                                                                                                   |

| 3.3) Conclusions                                                                                                             |

| CHAPTER 4 : IMPROVED PERFORMANCE IN H-BN ENCAPSULATED MOS <sub>2</sub> FETS<br>CONTACTED BY HIGHLY DOPED GRAPHENE ELECTRODES |

| 4.1 Introduction                                                                                                             |

| 4.2 Experimental details, results and discussions                                                                            |

| 4.2.1) Fabrication of graphene contacted MoS <sub>2</sub> FETs encapsulated my h-BN47                                        |

| 4.2.2) Characterization of highly doped graphene                                                                             |

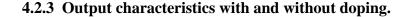

| 4.2.3) Output characteristics with and without doping                                                                        |

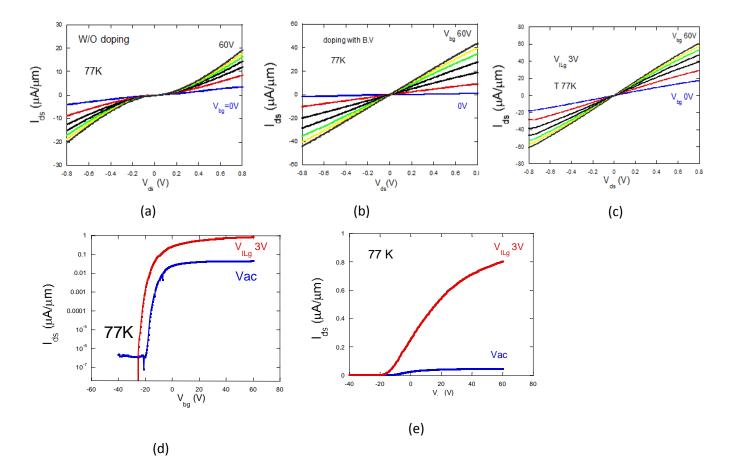

| 4.2.4) The transfer characteristics with and without doping                                                                  |

| 4.2.5) Four terminal measurements                                                                                            |

| 4.2.6) Important of h-BN passivation for better device performance                                                           |

| 4.3 Conclusions                                                                                                              |

| CHAPTER 5:COMPARISON OF PERFORMANCE WITH DIFFERENT CHANNEL DOPING LEVELS FOR WSE <sub>2</sub> FETS                           |

| 5.1 Introduction                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 Experimental details, results and discussion                                                                                      |

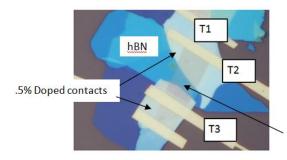

| 5.2.1) Fabrication of 2D/2D contacted slightly doped WSe <sub>2</sub> FETs encapsulated by h-BN58                                     |

| 5.2.2) Electrical transport properties of degenerately (.5% Nb) doped WSe <sub>2</sub> (Nb <sub>0.005</sub> $W_{0.995}Se_2$ ) samples |

| 5.3 Transport properties of WSe <sub>2</sub> samples with different doping levels                                                     |

| 5.3.1) Characterizing the degenerately (.5% Nb) doped $WSe_2$ (Nb <sub>0.005</sub> $W_{0.995}Se_2$ ) samples                          |

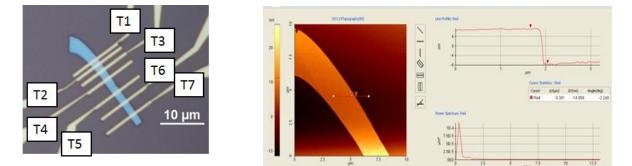

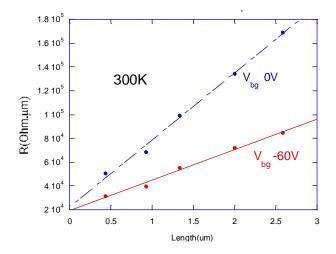

| 5.3.2 Transmission line measurements (TLM) for Nb <sub>0.0005</sub> W <sub>0.9995</sub> Se <sub>2</sub> samples62                     |

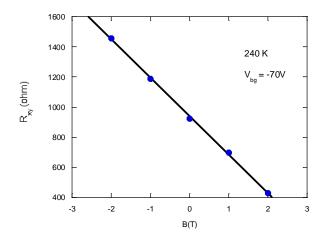

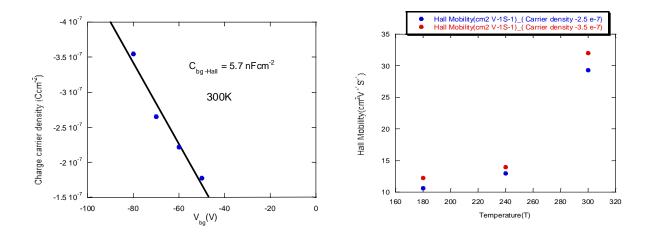

| 5.3.3 Hall bar measurements for $Nb_{0.0005} W_{0.9995}Se_2$ samples                                                                  |

| 5.4) Fabrication of 2D/2D contacted WSe <sub>2</sub> FETs for lightly doped channel                                                   |

| 5.5) Stable 2D/2D contacted .01% doped WSe <sub>2</sub> channel for excellent performance                                             |

| 5.6) Conclusions                                                                                                                      |

| CHAPTER 6 : SUMMARY AND FUTURE WORK75                                                                                                 |

| BIBLIOGRAPHY                                                                                                                          |

| ABSTRACT                                                                                                                              |

| AUTOBIOGRAPHICAL SATATEMENT                                                                                                           |

#### LIST OF FIGURES

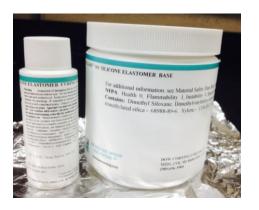

Figure 2.3:Sylgard 184 silicone curing agent and elastomer (respectively from left to right)

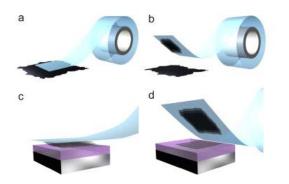

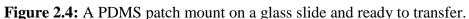

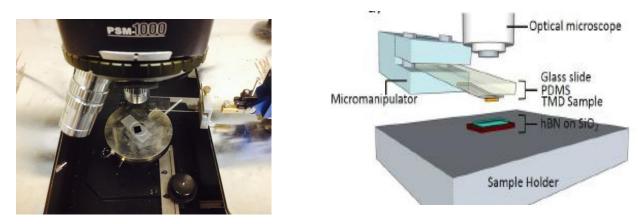

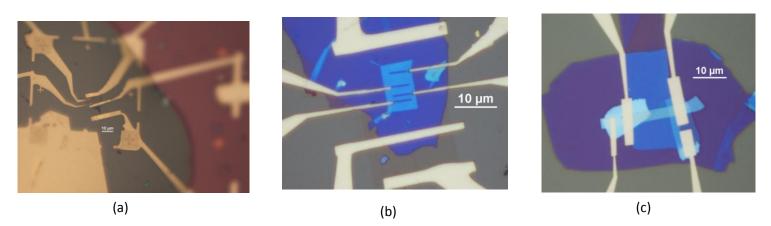

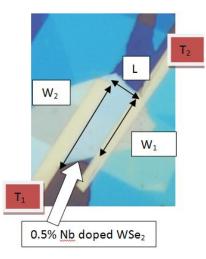

**Figure 2.6:** The steps of fabricating 2D/2D contacted device. (a) Bottom h-BN dielectric transferred on SiO<sub>2</sub> substrate. (b) Nb<sub>0.0001</sub>  $W_{0.9991}$ Se<sub>2</sub> transferred on h-BN (c) Top h-BN passivation for the channel (d) Transferring degenerately doped contacts (Nb<sub>0.005</sub>  $W_{0.995}$ Se<sub>2</sub>) as drain and source electrodes (e) Fabricating metal electrodes for the 2D/2D contacted device .....14

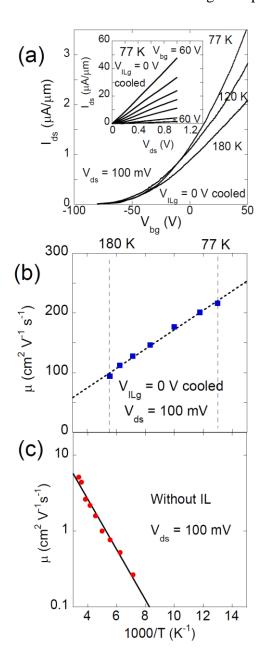

**Figure 3.3.** Comparison of the output characteristics of the trilayer  $MoS_2$  device used in Fig. 2, measured in the ionic-liquid-gate and back-gate (without ionic liquid) configurations. (a) Drain-source current  $I_{ds}$  as a function of the drain-source bias  $V_{ds}$  at ionic-liquid-gate voltages between -0.5 and 1 V. (b)  $I_{ds}$  as a function of  $V_{ds}$  at selected back-gate voltages between 0 and 60 V before the ionic liquid was deposited. The inset in (b) shows the magnified low-bias region in this panel.

**Figure 3.4.** (a) Transfer characteristics of the identical trilayer  $MoS_2$  device in two separate runs, where the ionic-liquid-gate voltage was swept at  $V_{ds} = 100 \text{ mV}$ ,  $V_{bg} = 0 \text{ V}$  and T = 250 K. (b) Transfer curves of the identical ionic-liquid-gate device measured at various back-gate voltages between 0 and 30 V. The inset in (b) shows the back-gate voltage *vs*. the threshold voltage of the transfer curves.

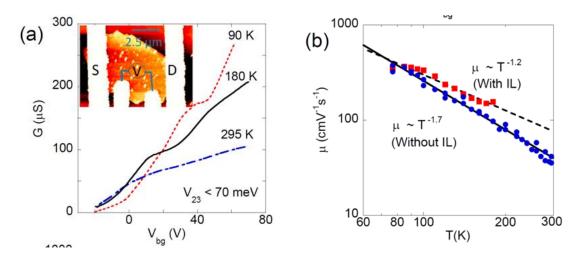

**Figure 4.4:** (a)The optical micrograph image of a four terminal graphene contacted  $MoS_2$  FET, using h-BN as bottom and top passivation dielectric. The scale bar is 10um.(b)4- probe conductivity as a function of  $V_{bg}$  for fixed temperatures without doping. (C) The four probe conductivity as a function of temperature. The blue data points correspond to device without doping and red data points mean device with Ionic liquid gating 3V ......60

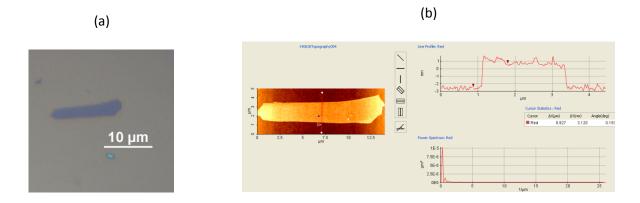

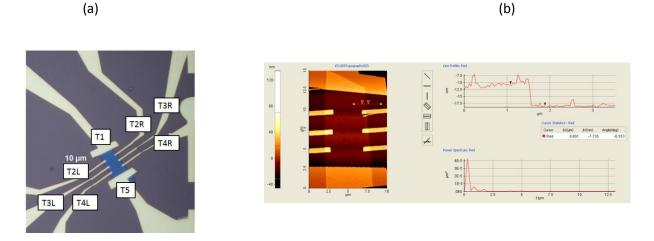

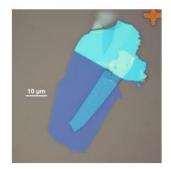

**Figure 5.3:** The AFM scanned images of the .01% Nb doped  $WSe_2$  samples.(a)The AFM image with the scale bar that represents the thickness of the sample which is around 5.6 nm in this case.(b) shows the 1.5 X 1.5 um<sup>2</sup> close analysis of the channel.. 67

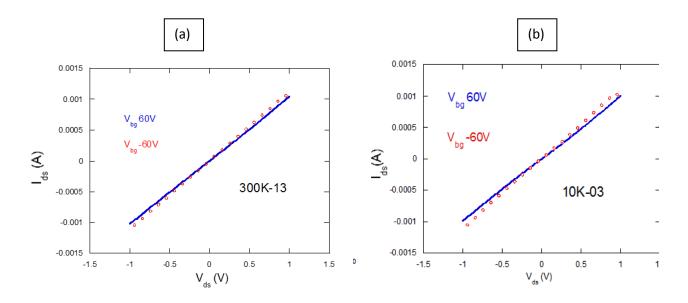

**Figure 5.4:**  $I_{ds}(V)$  Vs V<sub>ds</sub> for different fixed V<sub>ds</sub> from -60V to 60V for Nb<sub>0.005</sub> W<sub>0.995</sub>Se<sub>2</sub> contacts.(a) The contacts measures at 300K (b) The contacts were measured at 10K ... 69

**Figure 5.5:** a) Optical micrograph of a device structure for TLM measurement consisting of a ~ 18 nm thick degenerately *p*-doped WSe2 (Nb<sub>0.005</sub> W<sub>0.995</sub>Se<sub>2</sub>) with Ti/Au metal contacts. Normalized total resistance as a function channel length measured at room temperature (**b**), and 5 K (**c**). (**d**) Drain-source current as a function of drain-source voltage at  $V_{bg} = 0$  V ......70

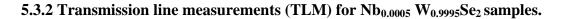

| <b>Figure 5.6:</b> (a) Optical micrograph of a device structure for TLM measurement consisting of a ~ 15nm thick Nb <sub>0.0005</sub> $W_{0.9995}$ Se <sub>2</sub> with Ti/Au metal contacts. (b) The AFM image of the transmission line with the height distribution                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.7: Normalized total resistance as a function of channel length measured at room temperature                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Figure 5.8:</b> (a)The optical micrograph of Hall bar device (b) The AFM image of the Hall bar device and it's thickness variation across the channel                                                                                                                                                                                                                                                                                                                             |

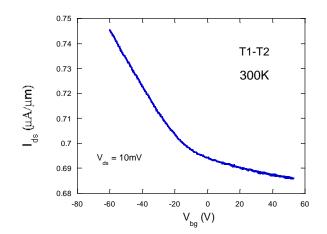

| <b>Figure 5.9:(a)</b> The I-V curves at 300K for the Two probe field effect mobility for $T_{67}$ electrode pair.(b) Two probe transfer curve for different bias voltages at 300K                                                                                                                                                                                                                                                                                                    |

| <b>Figure 5.10 :(a)</b> Carrier density extracted from Hall effect measurement as a function of back gate voltage at 300 K to determine the back gate capacitance. (b)Temperature dependence of Hall mobility for two different carrier concentrations                                                                                                                                                                                                                               |

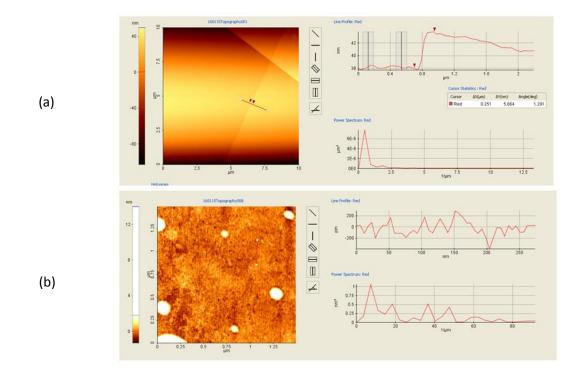

| <b>Figure 5.11 :</b> The transport properties of .5% Nb doped contacted (two probe) $WSe_2$ FET with .01% channel doping.( <b>a</b> ) $I_{ds}$ Vs $V_{bg}$ at 300K for fixed $V_{bg}$ from -20V to -100V. ( <b>b</b> ) The linear version of the coductivity transfer curves of the device at 300K for both $V_{ds} = -50V$ and $-1V$ . ( <b>c</b> ) The logarithmi version of the same transfer curves.( <b>d</b> ) The schematic band diagramme to explain how 2D/2D contacts work |

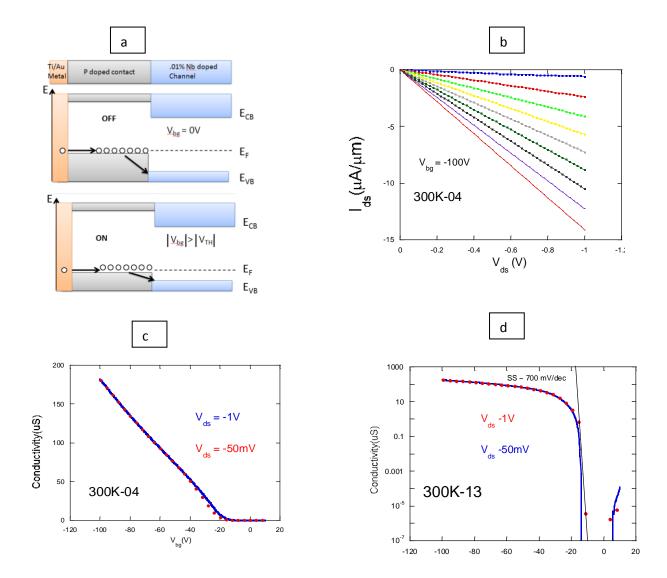

| <b>Figure 5.12:</b> The observed intrinsic transfer properties of 2D/2D contacted slightly doped WSe <sub>2</sub> FETs (a) The temperature dependence of two probe conductivity at $V_{ds} = -1V$ (b) The output characteristic for the range of $V_{ds} = -0.04V$ to $0.04V$                                                                                                                                                                                                        |

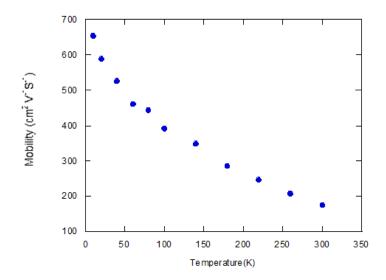

Figure 5.13: The two terminal field effect hole mobility as a function of temperature......80

## **CHAPTER 1:GENERAL INTRODUCTION**

#### 1.1 Development of 2D materials beyond Graphene

Two dimensional(2D) materials have demonstrated a wide range of remarkable properties for applications in next generation nano-electronics. Their atomic scale thickness provides higher degree of electrostatic control than bulk materials[1], revealing the possibility for low power electronics devices[2].To date, the most widely studied 2D material is graphene due to its rich physics and potential in device applications including electronics [3, 4], spintronics[5, 6], chemical and biological sensing [7-10], nano-electromechanical systems (NEMS) [11], and energy storage [12]. However graphene does not have a band gap that limits its applications in digital logic devices. A band gap in graphene can be generated by applying high transverse electric fields in bi-layer graphene or shaping graphene into nano-ribbons. However these efforts increase the complexity for device fabrication and also lead to mobility reduction.[13]

Alternatively, another class of 2D materials known as, transition metal dichalcogenides -TMDs (such as MoS<sub>2</sub>, MoSe<sub>2</sub> and WSe<sub>2</sub>) have not only demonstrated many of the "graphene like" properties desirable for electronics applications such as mechanical flexibility, chemical and thermal stability and the absence of dangling bonds, but also have a substantial band gap. As the most studied TMD material to date, MoS<sub>2</sub> has a band gap of  $\sim 1.8$  eV, which makes it a suitable candidate for low power digital logic devices [14]. Just like graphene, TMD materials can be exfoliated from its bulk crystals by mechanical exfoliation method due to the weak van der Waals interactions between layers.

#### 1.2 Challenges in 2D materials based electronics.

#### **1.2.a)** Understanding the main challenge

In the early studies of "graphene like" 2D semiconductor, the carrier mobility of few layer and monolayer MoS<sub>2</sub> FETs fabricated on Si/SiO<sub>2</sub> substrates was calculated to be in the range of 0.1-10 cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup>. This is orders of magnitude lower than the mobility of graphene. Moreover, it substantially lower than the phonon-limited mobility in bulk MoS2 crystals (which is on the order of 100 cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup>) [15-18]. In one study by Radisavljevic*et al.* the mobility of monolayer MoS2 was imprved significantly using HfO2 high -к dielectric top gating. This was attributed to the screening of Coulomb scattering and modification of Phonon dispersion[19]. In addition to higher mobility,  $MoS_2$  FETs have demonstrated high ON-OFF ratio(10<sup>8</sup>), near ideal sub threshold swing (74 mV/decade) and outstanding mechanical flexibility, opening up its ability to use in low power and high performance flexible devices [19-21]. Furthermore MoS<sub>2</sub> FET can be used in novel applications such as as energy harvesting [22, 23] and optoelectronics [24, 25] devices. However, it is not completely clear, to what degree the reported charge impurity screening and phonon dispersion modification contributes to the mobility improvement. On the other hand, a studiesbyGhataket al. and Lee et al. suggest that the low mobility values reported for MoS<sub>2</sub> FETs fabricated on Si/SiO<sub>2</sub> are largely due to the charge- impurity-induced electron localization [16] and Schottky barrier forms at  $MoS_2$  /metal contact interface respectively [26]. A study by Lin *et al.* shows that mobility increase in polymer electrolyte covered monolayer MoS<sub>2</sub> FETs can be attributed partially to the reduction of contact resistance and partially to the enhancement of the channel mobility [27].

#### **1.2.b)** Contact engineering as a solution

The strength of semiconducting 2D TMDs such as MoS<sub>2</sub>, MoSe<sub>2</sub> and WSe<sub>2</sub> as channel materials lies in their large bandgap, which results in a very high ON-OFF current-ratio and excellent electrostatic integrity [14]. However, large bandgap semiconductors are also known to have difficulties forming Ohmic contacts with metal, while low resistance Ohmic contacts are essential in optimizing the device performance of FETs.

There are typically two types of low resistance Ohmic contacts that can be made between a semiconductor and a metal, (a) very low barrier Schottkycontacts and(b) tunneling contacts. Ideally, an Ohmic contact can be formed if the SB height is zero or negative. For an n-type semiconductor such as  $MoS_2$  and  $MoSe_2$ , the work function of the metal must be close to or smaller than the electron affinity of the semiconductor to form Ohmic contacts. Bulk  $MoS_2$  as a n-type semiconductor has an electron affinity of ~ 4 eV, and that of atomically thin  $MoS_2$  is expected to be even smaller due to the increased band gap[26, 28]. However, the work function of most commonly used electrode metal ranges from slightly over 4 eV for Al andTi to over 5 eV for Pd and Ni.

In addition, a good electrical contact material also requires high conductivity, chemical, thermal, electrical stability. It is extremely difficult to have stable electrical properties if low work function metals (such as Ca, which has a work function of 2.9 eV) are used, since low-work-function metals oxidize easily, which severely degrades their electrical characteristics. Therefore, it is challenging to find a suitable metal to form very low barrier Schottky contacts to n-type TMDs. For a p-type semiconductor such as WSe<sub>2</sub>, the work function of the metal must be close to or larger than the sum of the electron affinity and the bad gap energy, which is similarly

challenging. Although relatively good contacts have been made between the p-doped monolayer  $WSe_2$  and the high work function Pd, a non-negligible SB still appears to be present [29]. Furthermore, the Schottky barrier in reported  $MoS_2$  FET devices with various metal contacts appears to be quite insensitive to the work-function of the contact metal, suggesting the presence of Fermi level pinning (or at least weak pinning) likely due to the metal induced gap states at the metal/MoS<sub>2</sub> interface [30].

#### **1.3 Methods to reduce contact resistance**

#### **1.3.1)** Metal contacted MoS<sub>2</sub> FETs with Ionic liquid gating.

Aconvenient way to make low -resistance contacts is to make narrow Schottky junctions, where the contact resistance is determined by the tunneling current. As our first approach to improve the contacts of MoS<sub>2</sub>FETs,we used Ionic Liquid (IL) gating which forms an electric double layer with high capacitance at MoS<sub>2</sub>/metal interface. As a result, IL gated MoS<sub>2</sub> FETs demonstrate high tunneling efficiency and thus low contact resistance due to the strong band bending occuring at MoS<sub>2</sub>/metal interface. We successfully observed mobility enhancement, higher ON-OFF ratio for both electrons and holes, near ideal sub-threshold swing and phonon limited behavior.

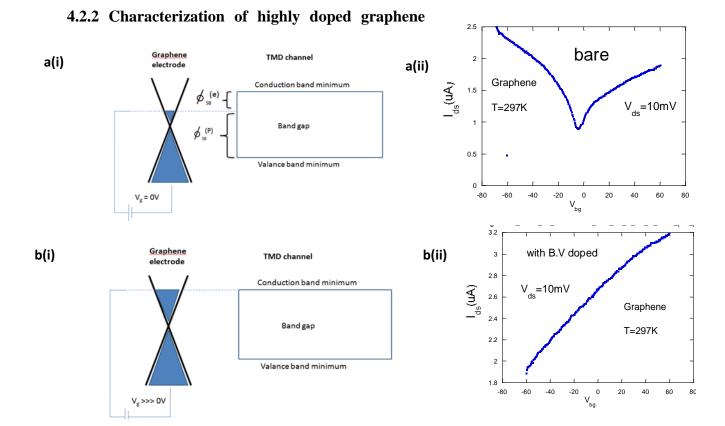

#### 1.3.2) Highly doped graphene as low-resistance contact material for MoS<sub>2</sub> FETs.

According to Yu *et al.* the work function of graphene can be tuned by electric field effect within the range of 4.5 -4.8 eV for single layer and 4.65-4.75 eV for bilayer graphene using a Si back gate with a 300 nm thick SiO<sub>2</sub> dielectric layer, making graphene an attractive material for low contact barrier electrodes [31]. However, significantly larger range of work function tunability will be needed for achieving true Ohmic contacts for both electrons and holes in

graphene/TMD junctions due to the large band gap of the TMD materials. To resolve this issue, we used ionic liquid gates to more effectively tune the carrier density (thus the work function) of graphene. An ionic liquid gate can induce a high carrier density exceeding  $10^{14}$  cm<sup>-2</sup> in graphene, which is more than an order of magnitude higher than using a conventional solid-state gate dielectric [32]. Atomically sharp interfaces between graphene and hydrogenated Si as well as between graphene and MoS<sub>2</sub> have been achieved, and a modulation of SB at the graphene/Si junction by a gate voltage has also been demonstrated [33, 34]. The nearly ideal diode ideality junctions factor observed in graphene/Si strongly suggests that high quality graphene/semiconductor contacts free of interface states are achievable using graphene as a contact-electrode material [33].

Furthermore we used Hexagonal Boron Nitride (h-BN) as a bottom dielectric and channel passivation material. The main reason of the channel passivation ids to selectively dope graphene contacts by protecting the channel. h-BN is used due to its atomically smooth surface, which is chemically inert and relatively free of charged impurities and charge traps [35-37].

#### 1.3.3) 2D/2D contacts with slightly doped channel.

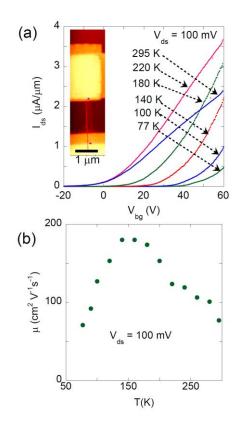

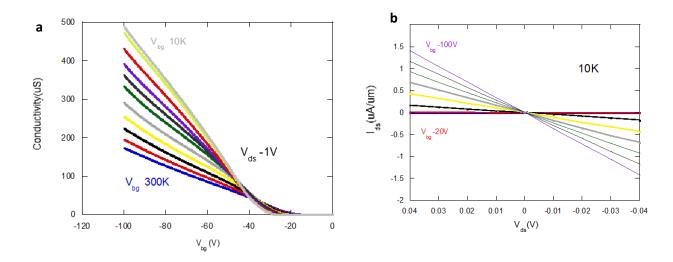

For realistic device applications, more permanent, air and thermally stable Ohmic contacts with lower contact resistance are needed. In this respect, we used degenerately doped 2D electrodes along with lightly doped 2D channel. Nb is used as p-dopent and is bound with covalent bond which provides higher air and thermal stability[38]. 2D /2D junctions can be formed with atomically smooth surfaces by Van der Waals assembly of 2D crystals[39, 40]. In this study the .01% Nb (Nb<sub>0.0001</sub> W<sub>0.9991</sub>Se<sub>2</sub>) doped WSe<sub>2</sub>was used as the channel material and .5% (Nb<sub>0.005</sub> W<sub>0.995</sub>Se<sub>2</sub>) degenerately doped samples for contacts. The obtained transport

5

characteristics include a two probe field-effect mobility of ~  $180 \text{ cm}^2 \text{V}^{-1} \text{S}^{-1}$  at room temperature, which increases up to around 700 cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup> at 10 K. We also observed near 10<sup>8</sup> ON/OFF ratio, intrinsic phonon limited behavior and subthreshold swing of 700 mV/dec at room temperature.

## **CHAPTER 2:EXPERIMENTAL METHODS**

In order to achieve higher device performance and intrinsic transport properties for TMDs based FETs, we employed novel contact engineering strategies. This chapter is describes techniques that were used to fabricate devices with each different contact engineering strategies. In addition to standard FET fabrication techniques, we have used a home-built transfer stage to fabricate TMD FETs with 2D contacts.

#### 2.1 Substrate cleaning

The first of the device fabrication process is to prepare clean Si/SiO<sub>2</sub> substrates.For this purpose, degenerately doped Si wafers with 270-290 nm thickSiO<sub>2</sub>are used as the substrates. When mechanically exfoliated TMDs are transferred on to these substrates, the above mentioned oxide thickness range provides high visibility for monolayer or few layer samples. To remove the particulates on the Si/SiO2 substrates, they were sonicated in Isopropyl Alcohol (IPA) andacetone for 10 minuteseac, where the ultra sonic waves are used to loosen the particles adhering to the surfaces.

Once this is done, thesubstrates are annealed in the annealer at  $600^{\circ}$ C for 10 minutes in forming gas(90% Ar and 10% H<sub>2</sub>) and cooled down gradually. This helps to eliminate organic residues on the substrate surfaces and thus to thoroughly clean the substrate.

#### 2.2 Sample fabrication with mechanical exfoliation

Next step is to synthesis TMD materials. Ultimately we measure the intrinsic transport properties of TMD channel materials after improvements in contacts. To make sure we get the best TMD channel material, it's necessary to produce clean, uniform high quality samples.TMDcrystals are composed of vertically stacked layers which are interacting weakly and held together by Vander Waals interactions.[2]

8

TMDs can be exfoliated into single or few layers by using mechanical exfoliation method.[41] First we place a tiny piece of 2D material on the ultralow residue tape (Ultron system R1007 tape). Then another piece of tape is placed on 2D material and press it using an eraser or thumb.[41]Keeping the bottom tape fixed, slowly peel off the top tape maintaining an angle. Repeat this several times until MoS<sub>2</sub> is thinner enough.[41] Once you have thin enough flakes on the tape, transfer them onto Si/SiO<sub>2</sub> substrates. This will give flakes with wide range of thickness distribution.We can look for samples with desired thickness range under the optical microscope.[41] MoS<sub>2</sub> mono-layers were transferred to degenerately doped silicon substrates covered with 270-nm-thick SiO<sub>2</sub> (Fig. 2.1).

Figure 2.1 : Mechanical exfoliation of 2D material crystals.

To further characterize the  $MoS_2$ samples, they are scanned with non contact mode AFM (Park System XE-70) to understand the quality of the sample surface and measure the sample thickness. AFM is a powerful characterization tool that can provide resolution down to sub Å scale measurements. Figure 2.2 shows an optical micrograph of  $MoS_2$  sample and it's further characterized AFM image with sample height distribution.

Figure 2.2: (a) A bilayer  $MoS_2$  sample on  $SiO_2$  substrate. (b) An AFM image of a sample and it's thickness distribution.

Transferring TMDs directly on to Si /SiO<sub>2</sub>substrate was used in the early stage of our research efforts(Chapter 3).Over the time hexagonal Boron Nitride (h-BN) was used as a bottom dielectric to provide an atomicallysmooth surface that is chemically inert and relatively free of charged impurities and charge traps.[42]Furthermore, h-BN was used as a channel passivation layer to selectively dope graphene contacts that will be discussed in detail in chapter 4.In order to transfer h-BN and 2D contacts (will be discussed in chapter 5) we needed a method that can transfer 2D material to a targeted place on the substrate.This challenge was addressed by dry transfer method.A home built setup was used for this purpose and step by step explanation is presented below.

#### 2.3 Dry transfer method

Dry transfer method is extremely important technique which allows to fabricate devices that needed multiple 2D material transfer steps. For instance a typical 2D/2D contacted devices (which will be covered in chapter 6), need this method to transfer h-BN bottom dielectric, the TMD channel, The top passivation and 2D contacts for both drain and source. To transfer a 2D material on to a substrate, we first have to exfoliate the sample on to a Polydimethylsiloxane (PDMS) patch. PDMS is asilicone based polymer, and for this transfer procedure it's used as an intermediate material for transferring process. This means 2D materials are exfoliated on to PDMS and then transferred on a substrate.

#### 2.3.1) Preparing PDMS.

In-order to make high quality devices it is crucial to use freshly made PDMS. By doing so, we make sure that PDMS residue won't be introduced to the samples. PDMs is prepared using Sylgard 184 silicone elastomer base and curing agent. 7g of elastomer base is added to a freshly chosen plastic cup. Then 0.7 g of curing agent is added and stir using fresh, clean stick until they mixed well. This mixture is placed inside the vacuum for 20 minutes until all the bubbles are gone from the mixture.

Then use a brand new wafer, pour the mixture in to the center and spin coat it with 350 rpm for 35 seconds. Then the pre-coated PDMS should be backed on a hotplate for  $80^{\circ}$ C for 30 minutes and another 30 minutes to cool down.

Figure 2.3:Sylgard 184 silicone curing agent and elastomer (respectively from left to right)

#### 2.3.2) Preparing for the transfer.

First the 2D material that we want to transfer has to be exfoliated on to blue tape. Once it was exfoliated up to desired thickness, we look it under the optical microscope and choose a better area. Then we cut PDMS into small patches and place couple of patches on the area of the blue tape that already selected. Then put back the backing of the blue tape and press gently .Transfer the PDMS patches on to a glass slide and search for better samples under the microscope.

Once you find the patch with desired sample, it should be placed on a glass slide(Figure 2.4) along it's shorter edge. This will help to land the sample easily on the targeted position. The farthest end of the PDMS edge from the sample is mount to the glass slide with a scotch tape.

#### 2.3.3) Transferring the samples onto substrate.

For transferring we use a transfer stage with a micromanipulator. The transfer stage contains the microscope, a sample stage and a micromanipulator. The slide with the sample patch should be mount on to the micromanipulator as facing the sample towards the sample stage. The substrate should be mount on the stage. Then the glass slide brings on top of the substrate and lower towards the substrate looking from the microscope. When the sample on PDMS is so close to the substrate then we should lower the sample on PDMS patch slowly until

it completely land on the desired target. Finally we lift the glass slide very slowly until it completely off from the substrate. Now we can have a look under the microscope the sample that we have transferred.

Figure 2.5:(a) A real image of the transfer stage set up.(b) A schematic diagram of the ready to use transfer stage.

The following figure elaborates the transfer of each 2D material components in fabricating a 2D/2D contacted device.

Figure 2.6: The steps of fabricating 2D/2D contacted device. (a) Bottom h-BN dielectric transferred on SiO<sub>2</sub> substrate. (b) Nb<sub>0.0001</sub> W<sub>0.9991</sub>Se<sub>2</sub> transferred on h-BN (c) Top h-BN

passivation for the channel (d) Transferring degenerately doped contacts ( $Nb_{0.005} W_{0.995}Se_2$ ) as drain and source electrodes (e) Fabricating metal electrodes for the 2D/2D contacted device.

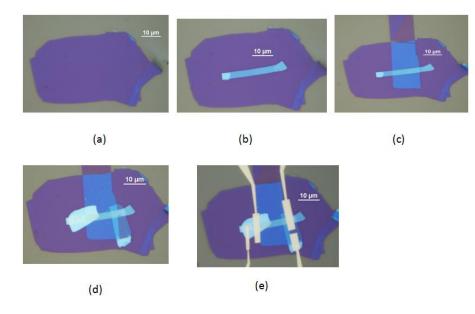

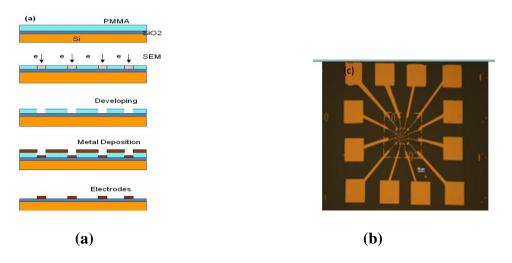

#### 2.7 Electron beam lithography and metal deposition

Electron beam (e- beam) lithography is a widely used, simple and reliable technique to fabricate nanodevices. A mask (resist) is used to cover the substrate which contains the sample and electron beam is used to pattern customized electrodes. Exposing the resist to electron beam changes the solubility of the resist in the exposed area.

Bilayer resist system is used in our standard e-beam lithography procedure. Two PMMA layers we use are 495 A4 and 950 A2, which have different molecular weights (represented by 495 /950) and concentrations (A4/A2). As the top layer, 950 A2 is used. This is mainly due to its less sensitivity to electron beam since it has higher molecular weight. This creates an undercut profile. PMMA is coated on the substrate using spin coating. A program with 4000 rpm for 45 seconds was used for this purpose. The first PMMA layer to coat is 495 A4which gives around 220 nm of thickness while 950 A2 gives around 80 nm.After each coating step, the substrate is baked in 180°C for 5 minutes. Then silver paint is applied close to the sample area, to fine focus the system before writing the pattern. NPGS (Nano Pattern Generating System) software is used to design and customize the pattern that we need to write. The written patterns have to be developed afterwards. This means the resist will be removed only from the area that was exposed to electron beam, following the designed customized pattern. After writing the pattern using e beam lithography, the very next step is developing, which removes the resist from area that was exposed to e-beam. Developing involves soaking the e-beam patterned sample in 1:3 mixture of MIBK:MEK. Finally the sample is observed under the microscope and take images in different magnifications.

Then we deposit Ti/Au combination on the exposed area using standard metal deposition process. Finally we remove the remaining resist by soaking the sample in Acetone which is called lifting off, and end up with having metal electrodes as we designed. The whole purpose of this procedure is to create electrodes on the TMD samples which are on the Si substrate and construct FETs.

**Figure 2.7:(a)** Schematic diagram of PMMA resist on  $SiO_2$  /Si substrate. (b) E beam lithography to create patterns on the resist.[43]

#### 2.7.1) The main steps of E-beam lithography process

#### **Film preparation**

- 1. Substrate cleaning example procedure (for Silicon substrate):

- (a) Sonicate in Acetone for 20 min;

- (b) Sonicate in IPA for 10 min;

- (c) Annealing at  $600^{\circ}$ C for 10 minutes. (Add Ar gas for 2 minutes during this

time)

- 2. Substrate bake: 150° C for 30 minutes on hotplate

- 3. PMMA spin: refer to the specific PMMA data sheet (e.g., 495 PMMA A4 3000 rpm film

```

thickness ~ 200 nm)

```

- 4. Film bake: refer to the specific PMMA data sheet (e.g., 180°C for 1~1.5 min on hotplate for 495 PMMA)

- 5. Make a scratch on the sample surface as a reference mark for e-beam adjustment and patterning.

Specimen and SEM Setup

- 1. Load the sample into the SEM.

- 2. Optimize sem.

- 3. Focus on gold particles.

- 4. Move to appropriate area.

- 5. Focus on silver particle for fine tuning.

- 6. Using appropriate program write the pattern on the substrate.

#### **2.7.2) Pattern Development**

- Check the PMMA Data sheet for proper development conditions. Below are several sample procedures for your references. Developer Time Conditions MIBK:IPA 1:3 70 seconds for more sensitive features MIBK:IPA 1:1 70 seconds for larger features (stronger developer) IPA 20seconds

- 2. Dip the sample into the proper developer solution and swirl constantly for a desired period of time (e.g., 70 seconds).

- 3. Dip the sample into pure IPA solution or DI water and swirl for 20 seconds to stop the reaction.

- Quickly wash the substrate with water and dry with Nitrogen gas. Decrease the flow of Nitrogen gas if necessary (for sensitive features).

- 5. Pour the developer and IPA into proper waste storage containers under the hood.

- 6. Check the pattern under the optical microscope.

#### **2.8) Metal Deposition**

The metal deposition allows to form metal electrodes on the patterns we wrote using lithography. We need to make sure that metals we are using have smaller work functions in order to get good n channel contacts with  $MoS_2$  sample since it forms smaller Schootky barrier.

For metal deposition, Termescal model BJD-1800 E-beam evaporator was used. This includes high vacuum chamber, pumping system (mechanical pump, diffusion pump and automated interlocks) and sources to be targeted by E-beam.[44] In this particular equipment we have 6 pockets to hold sources. The samples should be loaded in to the system and have to wait round 2 hours until the system reaches the pressure lower than 2 X  $10^{-6}$  torr to start the deposition. For out samples we usually use 10nm Ti and 40nm Au as deposition metals. The rate of deposition is used as 1 Å/s for both materials.

Figure 2.8: BJD 1800 E-beam evaporation system for metal deposition[44]

The source metal is evaporated in vacuum and vapor particles move towards the target, condensed back and deposit.[45]Following figure shows the schematic diagrams to illustrate the processes with respect to electron beam lithography and metal deposition. In the next image, the electrodes are shown in after lift-off process using acetone.

**Figure 2.9:** The schematic diagrams show the integrated processes with electron beam lithography and metal deposition. (a) Starting the coating of PMMA to lift-off process. (b) The actual electrodes picture ready for electric measurement.

#### 2.8.a) Annealing process

To remove any absorbed impurities from the 2D materials and improve the qulaity of performance, thermal annealing is used. In device fabrication, this helps to reveal the true electrical transport properties of the channel and improve the contacts. In our fabrication process, we used two types of annealing procedures. To clean the Si substrates, the maximum temperature of 600°C for 10 minutes with purging gas (10% Ar and 90% H<sub>2</sub>) were used. For this purpose (Ulvac Mila 5000 equipment )was loaded with the Si substrates , turn on the vacuum pump and purge with purging gas for three times. When the annealer starts running ,it reaches the maximum temperature of  $600^{\circ}$ C and stays there for 10 minutes. During this window, we let

purging gas in for 2 minutes. After staying 10 minutes, the annealer starts to drop its temperature gradually and reach the room temperature. This completes the annealing process for Si substrates. We usually perform this prior to use the Si substrates.

When it comes to anneal fabricated TMD FETs, we make sure to use the maximum temperature of 250°C for 30 minutes. In this case we don't let the purging gas in when it reaches the maximum temperature.

Figure 2.12:Ulvac Mila 5000 annealer

#### **2.9) Doping methods.**

After devices are fabricated ,different doping methods are used as contact engineering approach to improve device performance and achieve intrinsic transport properties.

#### 2.9.1) Ionic Liquid (IL) doping.

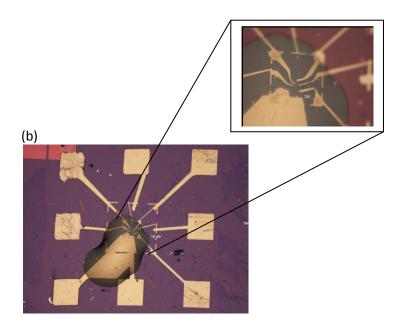

Ionic liquid is binary organic salts that can foam an electric double layer at IL/Channel interface[46]. This acts like a parallel plate capacitor. Once the devices are fabricated, small droplet of DEME-TFSI IL (Supplied from Sigma Aldrich 727679) is applied using micro-manipulator. In order to apply IL gating efficiently we make sure that the IL drop covers the ing area (The contact area generally) with minimum spreading and the gate electrode with the maximum spreading. In the below we have a schematic diagram and a real image to demonstrate how it looks like after IL gating is applied.

**Figure 2.11:**An optical micrograph of a metal contacted  $MoS_2$  device after application of IL gating at 10X and 50 X magnification.

#### 2.9.2) Benzyl Vioilogen doping method

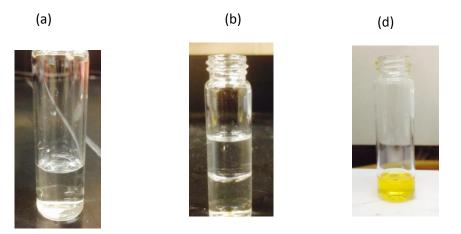

Air stable doping of 2D materials is really important for electronic and optoelectronic applications as well as to understand the intrinsic channel bahvior by improving the contacts.[47] Benzyl Viologen (B.V) is a surface charge transfer donor which can be used to dope graphene or other TMDs. In our study we use B.V to highly dope the electrodes of grapehe contacted  $MoS_2$  FETs. According to the literature  $MoS_2$  can be doped up to the degenerate doping level using B.V doping method.[47]This method is even attractive since the B.V can easily spin coat on the device and can be reversibly removed using Toluene.[48]

The B.V solution is prepared as follows. First 8 mg of Benzyl Violgen dichloride (powder) is measured and put in to a clean small bottle. Then 2.5 ml of De-ionized water (D.I

Water) is added in to the same bottle. Then the mixture of B.V powder and D.I water is shaked gently until they mixed properly. Once the B.V powder is dissolved completely the final solution looks colorless(Figure 2.10 (a)).Then 2.5ml of Toluene is added to the prepared B.V solution using a pipette. Toluene doesn't dissolve with the prepared B.V mixture, so it forms as a layer on Top.(Figure 2.10(b)).Then 50 mg of Sodium Borohydride (NaBH<sub>4</sub>) is added to the solution (Figure 2.10(c)).This first enters to the Toluene layer and start to react with the B.V solution in the bottom. This is kept for a day and the top Toluene layer is extracted by a pipette and put in a clean container.(Figure 2.10 (d)).For a B.V solution prepared with above mentioned recipe, we will get a B.V solution with 60mM concentration.

**Figure 2.10:** The step by step preparation process of B.V solution.(a) B.V powder is mixed with D.I water (b) After Toluene is added (c) Right after NaBH<sub>4</sub> is added (d)After extracting Toluene layer with B.V which is ready to use for doping

#### 2.10) The summary of devices types that are fabricated for each project

**Figure 2.13 :**The type of contact engineering approaches used to improve device performances. (a) Metal contacted  $MoS_2$  FET with IL gating (b) The highly doped graphene contacted  $MoS_2$  FET with h-BN passivation (c) 2D/2D contacted WSe<sub>2</sub> FET with h-BN passivation.

# CHAPTER 3 : IMPROVED PERFORMANCE IN FEW LAYER MOS<sub>2</sub> FETs VIA IONIC LIQUID GATING.

#### **3.1 Introduction**

In the quest for flexible electronics in the "post-silicon" era, graphene has attracted much attention due to unsurpassed carrier mobility and high thermal conductivity,[49-52] combined with excellent chemical and thermal stability down to the nanometer scale.[53] The major drawback is the absence of fundamental band gap, which makes semimetallic graphene unsuitable for conventional digital logic applications. Sustained efforts to engineer a band gap in graphene have either caused severe mobility degradation or require prohibitively high bias voltages.[54-57]

Molybdenum disulfide (MoS<sub>2</sub>), a layered transition-metal dichalcogenide (TMD), has emerged as a viable alternative to graphene, as it combines a semiconducting gap with mechanical flexibility, chemical and thermal stability and absence of dangling bonds. The singlelayer MoS<sub>2</sub> consists of a molybdenum monolayer sandwiched between two sulfur monolayers. The fundamental band gap changes from an  $\approx$ 1.2 eV wide indirect gap in the bulk to a direct gap of  $\approx$ 1.8 eV in single-layer MoS<sub>2</sub>.[14, 58] Similar to graphene, single MoS<sub>2</sub> layers can be extracted from bulk crystals by a mechanical cleavage technique due to relatively weak interlayer interaction with an important van der Waals character.[15] Besides conventional field effect transistors (FETs), the use of MoS<sub>2</sub> has been proposed for applications such as energy harvesting[22, 23] and optoelectronics.[24, 25] Recently, integrated circuits based on MoS<sub>2</sub> transistors have also been demonstrated, which is a significant step toward the application of MoS<sub>2</sub> in high-performance low-power nanoelectronics.[59] However, the room temperature carrier mobility in single- and few-layer  $MoS_2$  FETs fabricated on Si/SiO<sub>2</sub> substrates was found to be very low, typically in the range of 0.1 -10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>.<sup>12, 17, 21</sup> This mobility is not only orders of magnitude lower than that of graphene, but also substantially lower than the phonon-limited mobility in the bulk system,[15-18, 30] which is of the order of 100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. The interface between the MoS<sub>2</sub> channel and the SiO<sub>2</sub> gate dielectric has been considered as one of the primary factors limiting carrier mobility.[16] A substantial mobility enhancement to over 200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> has been reported for HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> capped monolayer and multilayer MoS<sub>2</sub> FETs, respectively, which was attributed to high- $\kappa$  dielectric screening of charged impurities that reduces scattering at the channel/dielectric interface.[60, 61] There are also rising concerns that the mobility in these devices might have been substantially overestimated.[62]

For large band-gap semiconductors such as  $MoS_2$ , a significant Schottky barrier may form at the metal/semiconductor contact, yielding a high contact resistance.[14]<sup>.[63]</sup> Lee *et al.* showed in their study of  $MoS_2$  flakes produced by liquid exfoliation that the mobility in  $MoS_2$  FETs could be largely underestimated due to the Schottky barriers at the  $MoS_2$ /metal contacts.[64] In the presence of a substantial Schottky barrier, the extrinsic mobility is also expected to degrade with decreasing temperature due to the reduced thermionic emission current and thermally assisted tunneling current, as was recently observed by Ghatak*et al* in atomically thin  $MoS_2$ FETs.[16] In agreement with recent predictions,<sup>24</sup> Das *et al.* has demonstrated a significant mobility enhancement by reducing the Schottky barrier height using a low work function contact metal, which further indicates that the performance of  $MoS_2$  FETs can be strongly influenced by the metal/semiconductor contacts.<sup>26</sup> In order to optimize the performance of  $MoS_2$  FETs, it is crucial to use low resistance Ohmic contacts. There are typically two types of low resistance contacts that can be made between a semiconductor and a metal: (a) Schottky contacts with a very low barrier height and (b) highly transparent tunneling contacts. Ideally, an Ohmic contact can be formed if the Schottky barrier height is zero (or negative). Contacts with low Schottky barrier height ( $\approx$ 30 meV) have been achieved in multilayer MoS<sub>2</sub> by using Scandium as a low work function contact metal.[65] However, the tunability of the Schottky barrier height may be reduced by Fermi level pinning.[30] Alternatively, highly transparent tunneling contacts can be fabricated by heavily doping the semiconductor in the contact region. This approach fails for MoS<sub>2</sub>, since ionized impurity doping would substantially damage the structural integrity of the atomically thin channel. As an alternative, surface doping with strongly oxidizing NO<sub>2</sub> molecules has been used to narrow the Schottky barrier thickness for hole injection and thus reduce the contact resistance of WSe<sub>2</sub> FETs.[66]

In this article, we report electrostatic doping using an ionic-liquid (IL) gate as a viable approach to achieve low resistance  $MoS_2$ /metal tunneling contacts. We demonstrate(i) significant improvement in the performance of few-layer  $MoS_2$  FETs and (ii) high carrier mobility in the  $MoS_2$  channel that is limited by phonons. Ionic liquids are binary organic salts that can form electric double layers at the ionic-liquid/solid interface and thus act as nano-gap capacitors with extremely large capacitance. As we show in the following, the Schottky barrier can be drastically reduced in ionic-liquid-gated FETs (IL-FETs) of  $MoS_2$ . We observe a significant increase of the tunneling efficiency that can be attributed to strong band bending at the  $MoS_2$ /metal interface, provided by the thin electrical double layer with a high capacitance. As a result, our nanometer-

thick MoS<sub>2</sub> IL-FETs exhibit a significantly enhanced extrinsic mobility that exceeds 60 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at 250 K, in contrast to  $\mu$ <5 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> measured in the Si-back-gate configuration without ionic liquid. The MoS<sub>2</sub> IL-FETs further exhibit ambipolar behavior with a high current ON/OFF ratio exceeding 10<sup>7</sup> for electrons and 10<sup>4</sup> for holes, and a near ideal subthreshold swing (SS) of ~50 mV/decade at 250 K. More significantly, the mobility in few-layer MoS<sub>2</sub> IL-FETs increases from ~100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> to ~220 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> as the temperature decreases from 180 K to 77 K, which is in good agreement with the true channel mobility derived from our four-terminal measurements. The temperature dependence of the mobility behaves as  $\mu \sim T^{\gamma}$  with  $\gamma \approx 1$ , indicating that the mobility is predominantly limited by phonon scattering in this case.

### 3.2 Results and discussion

Atomically thin MoS<sub>2</sub> flakes were produced from a bulk crystal by a mechanical cleavage method and subsequently transferred onto degenerately doped silicon substrates covered with a 290 nm-thick thermal oxide layer.[15, 67] An optical microscope was used to identify thin flakes, which were further characterized by non-contact mode atomic force microscopy (AFM). In the present study, we focus on bilayer and few-layer (2-7 layers corresponding to 1.3-5 nm thickness) samples, since the yield of bilayer and few-layer flakes was found to be much higher than that of single-layer MoS<sub>2</sub>. Moreover, few-layer MoS<sub>2</sub> also tends to form lower Schottky barriers (thus smaller contact resistance) than single-layer samples.[30, 65]MoS<sub>2</sub> IL-FET devices were fabricated by first patterning the source, drain and gate electrodes, consisting of 5 nm of Ti covered by 50 nm of Au, using standard electron beam lithography and electron beam deposition.[56] A small droplet of the DEME-TFSI ionic liquid (Sigma Aldrich 727679) was then carefully applied onto the devices using a micromanipulator under an optical microscope,

covering the  $MoS_2$  layer and the source, drain and gate electrodes.[68] The ionic liquid gate forms by self-assembly. DEME-TFSI has been chosen for its large electrochemical stability window (>3 V at room temperature).

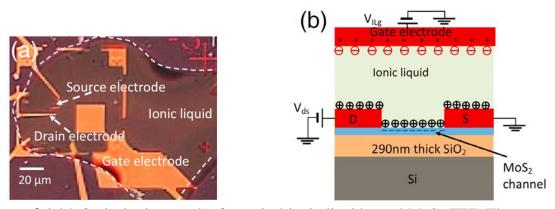

**Figure 3.1.(a)** Optical micrograph of a typical ionic-liquid-gated  $MoS_2$  FET. The contour of the ionic liquid drop covering the  $MoS_2$  channel and the in-plane gate-electrode are marked by white dotted lines. The scale bar is 20  $\mu$ m. (b) Schematic illustration of the working principle of an ionic-liquid-gated  $MoS_2$  FET.

Figure 3.1a shows a micrograph and figure 3.1b the schematic of a typical ionic-liquidgated  $MoS_2$  device. Electrical properties of the devices were measured by a Keithley 4200 semiconductor parameter analyzer in a Lakeshore Cryogenic probe station after dehydrating the ionic liquid under high vacuum (~1×10<sup>-6</sup>Torr) for 48 hours. This thorough removal of the remaining moisture turned out to be important to preventing the formation of chemically reactive protons and hydroxyls through the electrolysis of water.[69] Most measurements on ionic-liquidgated devices were carried out at 250 K or below to further reduce the possibility of any chemical reactions between the ionic liquid and  $MoS_2$ .[70] As shown schematically in figure 1.1b, negative ions in the ionic liquid accumulate near the gate electrode and positive ions accumulate near the  $MoS_2$  channel when a positive voltage is applied to an ionic-liquidgateelectrode near the device channel. The scenario reverses when a negative voltage is applied to the gate. In both cases, electric double layers form at the interfaces between the ionic liquid and solid surfaces.[71] To ensure that nearly all of the gate voltage appears as potential drop across the ionic-liquid/channel interface, the surface area of the gate electrode is 1-2 orders of magnitude larger than the total area of the transport channel plus parts of the drain/source electrodes, which are immersed in the ionic liquid.[72] Downscaling of the ionic liquid gated devices can be achieved by simultaneously reducing the surface area of the gate electrode and covering a large part of the drain/source electrodes with an insulating overlayer.[73]

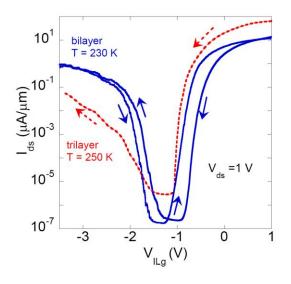

**Figure 3.2.** Transfer characteristics of representative bilayer and trilayer  $MoS_2$  ionic-liquid-gated FETs measured at the drain-source bias  $V_{ds} = 1$  V.

We have measured several ionic-liquid-gated bilayer and few-layer  $MoS_2$  FETs and observed consistent results. Fig. 3.2 shows the transfer characteristics of two representative devices measured at a drain-source voltage of 1 V. Both the bilayer and trilayer devices exhibit ambipolar behavior, with the current ON/OFF ratio exceeding  $10^7$  for electrons in both devices. The observed ON/OFF ratio for holes was  $10^6$  in the bilayer and  $10^4$  in the trilayer device. Ambipolar behavior has been previously observed in ion-liquid-gated thicker  $MoS_2$  flakes (>10 nm) by Zhang et. al.[70] However, their ON/OFF ratio was less than 10<sup>3</sup> for both electrons and holes, presumably due to the relatively large "OFF" state current passing through the interior of the crystal beneath the channel surface. This current ON/OFF ratio is much lower than the typical values between  $10^4$  and  $10^7$ , which are desired for digital logic devices.[60] It is worth pointing out that our observation of hole conduction in bilayer and few-layer MoS2 is rather surprising in view of the large Schottky barrier height (~1 eV) for the hole-channel.[30] Our results suggest that holes are injected into the MoS<sub>2</sub> channel primarily by thermally assisted tunneling rather than by thermionic emission.[74]The tunneling rate is increased significantly for both electrons and holes in presence of the extremely thin (~1 nm) dielectric layer formed by the ionic-liquid gate, which significantly reduces the thickness of Schottky barrier through strong band bending near the contacts at high gate voltages. Since the formation of an electrical double layer on the MoS<sub>2</sub> contacts near the edge of the metal electrodesis conformal, the thickness of the contact Schottky barrier can be reduced very effectively by the ionic liquid gate down to the electrostatic screening length in the ionic liquid (~1 nm).[75] The asymmetry between electron and hole transport can be attributed to

a larger Schottky barrier height for the hole channel that reduces thermally assisted tunneling,

a slight preference for the adsorption of positive ions on MoS<sub>2</sub>, as discussed later, and

intrinsic*n*-doping of the transport channel.

All of these effects tend to favor electron *vs*.hole transport, shifting the transfer curves toward the negative gate-voltage direction. The lower asymmetry between electron and hole transport (observed when the gate voltage was swept from positive to negative), causing a more balanced ambipolar character of the bilayer  $MoS_2$  device, may be attributed to a slightly lower degree of

intrinsic *n*-doping in the bilayer flake.[72] The hysteresis in the transfer characteristics could be attributed to the charge injection at the interfaces between the channel and the substrate as well as the slow motion of the ions at low temperature.[70, 76]

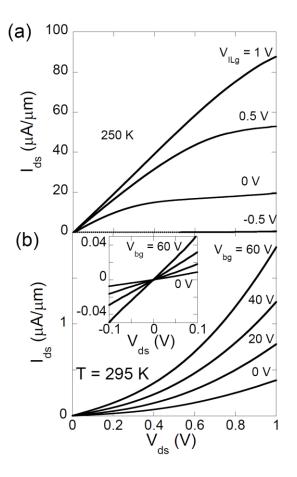

**Figure 3.3.** Comparison of the output characteristics of the trilayer  $MoS_2$  device used in Fig. 2, measured in the ionic-liquid-gate and back-gate (without ionic liquid) configurations. (a) Drainsource current  $I_{ds}$  as a function of the drain-source bias  $V_{ds}$  at ionic-liquid-gate voltages between -0.5 and 1 V. (b) $I_{ds}$  as a function of  $V_{ds}$  at selected back-gate voltages between 0 and 60 V before the ionic liquid was deposited. The **inset in** (b) shows the magnified low-bias region in this panel.

Low contact resistance is an important prerequisite to realize the full potential of  $MoS_2$  as a channel material for FETs. Since the Schottky barrier for holes is larger than for electrons, the contact resistance in the hole channel is higher than in the electron channel. To optimize the

device performance, we next focus on the electron channel only and study the impact of ionicliquid-induced Schottky barrier thinning on its electrical characteristics. Fig. 3.3 shows the output characteristics of a trilayer MoS<sub>2</sub> device that was measured both with an ionic-liquid-gate and a back-gate with no ionic liquid present. As shown in Fig. 3.3a, the drain current in the ionicliquid gate voltage range of 0<VILg<1 V exhibits linear dependence at low drain-source voltages and starts to saturate at higher  $V_{ds}$ . The current saturation at high  $V_{ds}$  can be attributed to the channel pinch-off of the FET. In sharp contrast to these data, the same device, when measured in the back-gate configuration without ionic liquid, exhibits strongly non-linear (upward turning)  $I_{ds}$ - $V_{ds}$  behavior, suggesting the presence of a significant Schottky barrier at the contacts (Fig. 3.3b). Furthermore, the total resistance calculated from the slope of the  $I_{ds}$  -  $V_{ds}$  characteristics in the low-bias region is over two orders of magnitude larger for the Si back-gate configuration  $(2 \times 10^6 \Omega \text{ at } V_{bg} = 60 \text{ V}$ , see the inset of Fig. 3.3b) than for the ionic-liquid-gate configuration  $(1 \times 10^4 \Omega \text{ at } V_{\text{ILg}} = 1 \text{ V})$ , providing further evidence that ionic-liquid gating significantly reduces the contact resistance by thinning the Schottky barrier. Note that linear  $I_{ds}$ - $V_{ds}$  dependence at small bias voltages ( $V_{ds}$ < 0.1 V, shown in the inset of Fig. 3b) is only a necessary, but not a sufficient condition for a low-resistance Ohmic contact. Linear current-voltage behavior may also be due to the thermally assisted tunneling current, especially at small drain-source voltages.[65]

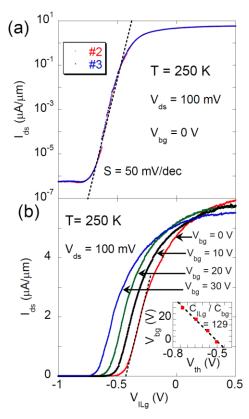

**Figure 3.4.(a)** Transfer characteristics of the identical trilayer  $MoS_2$  device in two separate runs, where the ionic-liquid-gate voltage was swept at  $V_{ds} = 100 \text{ mV}$ ,  $V_{bg} = 0 \text{ V}$  and T = 250 K. (b) Transfer curves of the identical ionic-liquid-gate device measured at various back-gate voltages between 0 and 30 V. The **inset in (b)** shows the back-gate voltage *vs*. the threshold voltage of the transfer curves.

The observed drastic reduction of the contact resistance by ionic-liquid gating opens up the possibility of investigating channel-limited device parameters in nanometer-thick MoS<sub>2</sub> devices. Fig. 3.4a shows the transfer characteristics from two separate measurements of the same trilayer MoS<sub>2</sub> device at T= 250 K, for  $V_{ds}$ = 0.1 V and  $V_{bg}$  = 0 V. The high reproducibility of the transfer curves indicate that charged ions in the ionic liquid are electrostatically accumulated at the gate/electrolyte and MoS<sub>2</sub>/electrolyte interfaces without any noticeable chemical reactions. The transfer characteristics also remain essentially unchanged at different gate voltage sweeping rates. Furthermore, the subthreshold swing (SS) reaches the theoretical limit of  $kT/e \ln (10) =$  50 meV/decade at T = 250 K corresponding to a gate efficiency of ~1. Such a high gate efficiency can be attributed to the large electric-double-layer capacitance of the ionic-liquid gate. The near ideal subthreshold swing also further indicates that the ionic-liquid gate creates highly transparent tunneling contacts.[77]

To extract the carrier mobility, we first estimated the ionic-liquid gate capacitance by measuring  $I_{ds}versusV_{ILg}$  of the same trilayer device at various fixed back-gate voltages, as shown in Fig. 4b. As the back-gate voltage is stepped up from the 0 to 30 V, the threshold voltage  $V_{th}$ of the  $I_{ds}$ - $V_{ILg}$  curves systematically shifts in the negative  $V_{ILg}$  direction, while the slope of the  $I_{ds}$ - $V_{ILg}$  curves remains nearly constant in the linear region. The small crossover between the  $I_{ds}$ - $V_{ILg}$  curve measured at  $V_{bg} = 30$  V and corresponding measurements at lower back-gate voltages may be due to the hysteretic effect. The ionic-liquid gate capacitance per unit area is estimated to be  $C_{\rm ILg} \sim 1.55 \times 10^{-6}$  Fcm.<sup>-2</sup> This estimate is based on the observed change of the threshold voltage  $\Delta V_{\rm th}$  in response to the change of the back-gate voltage  $\Delta V_{\rm bg}$  using the relationship  $C_{\rm ILg}/C_{\rm bg} = \Delta V_{\rm bg}/\Delta V_{\rm th}$ . We used  $C_{\rm bg} = 1.2 \times 10^{-8}$  Fcm<sup>-2</sup> for the capacitance per unit area between the channel and the back gate and the value  $\Delta V_{\rm bg}/\Delta V_{\rm th} = 129$ , determined from the linear fit shown in the inset of Fig. 4b. Using the expression  $\mu = L/W \times dI_{ds}/dV_{ILg}/(C_{ILg}V_{ds})$ , we estimated the lowfield field-effect mobility of ~293 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> using  $L=3.3 \mu m$  for the channel length and W=1.0 $\mu$ m for the channel width,  $dI_{ds}/dV_{tg}$  for the slope of  $I_{ds}$ - $V_{ILg}$  curve in the linear region at  $V_{bg} = 0$  V, and  $C_{\text{ILg}} \sim 1.55 \times 10^{-6} \text{ F/cm}^{-2}$ . Note that the value  $C_{\text{ILg}} \sim 1.55 \times 10^{-6} \text{ F/cm}^{-2}$  is about 4-5 times smaller than the  $C_{ILg}$  value determined by Hall measurements ( $C_{ILg,H} \sim 7.2 \times 10^{-6} \text{ Fcm}^{-2}$ ) on much thicker MoS<sub>2</sub> flakes[70]. The discrepancy may arise from the dependence of the quantum capacitance on the carrier density. The total capacitance  $C_{ILg}$ , consisting of the electrostatic

capacitance  $C_e$  of the electric double layer and the quantum capacitance  $C_q$  of the MoS<sub>2</sub> channel, which are connected in series  $(1/C_{ILg} = 1/C_e + 1/C_q)$ .  $C_{ILg}$ , is likely dominated by  $C_q$  due to the extremely large electrostatic capacitance of the DEME-TFSI ionic liquid gate,[69] which can be as high as 100  $\mu$ F/cm<sup>2</sup>. Since  $C_q$  is a measure of the average density of states (DOS) at the Fermi level, which increases with increasing carrier density, the value of  $C_q$  may also increase with the carrier density.[14] As a result, the  $C_q$  is expected to be smaller in the low carrier density region near the threshold voltage than in the higher carrier density region [above  $n_{2D} \sim 1 \times 10^{13}$  cm<sup>2</sup> as determined from  $n_{2D} = C_{ILg,H}(V_{ILg,H} - V_{th})$ ], where the field-effect mobility is determined. This may lead to a possible underestimate of the total capacitance and thus an overestimate of the mobility. Using the capacitance  $C_{ILg,H} = 7.2 \ \mu \text{Fcm}^{-2}$  determined by Hall measurement in multilayer flakes ( > 10 nm) at high carrier densities, the low limit of the field-effect mobility in our ionic-liquidgated trilayer  $MoS_2$  device is determined to be 63 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, consistent with the Hall mobility measured in ionic-liquid-gated MoS<sub>2</sub> multiplayer flakes and with the mobility of multiplayer  $MoS_2$  on  $SiO_2$  measured in a four-probe configuration.[70, 78] We conclude that the actual extrinsic field-effect mobility lies likely between 63 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and 293 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, which is 1-2 orders of magnitude higher than the mobility observed in typical Si-back-gated monolayer and few-layer MoS<sub>2</sub> FETs. This indicates the reported mobility ranging between  $0.1-10 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  in monolayer and few-layer MoS<sub>2</sub> FETs has been largely limited by the contact resistance. [15, 16, 60]

It is also worth noting that our ionic-liquid-gated MoS<sub>2</sub> channel is in a highly electrondoped state with a threshold voltage of  $V_{\text{th}} \approx 0.5$  V at  $V_{\text{ILg}} = 0$  V, which may be attributed to a higher concentration of positive than negative ions adsorbed in the vicinity of MoS<sub>2</sub>. A large negative threshold voltage shift was also observed in high- $\kappa$  dielectric passivated monolayer and multiplayer MoS<sub>2</sub> FETs, which could be attributed to the presence of a large amount of fixed positive charges in the dielectric layer, which have likely accumulated during the low temperature atomic layer deposition process.[60, 61] Similar to the molecular ions adsorbed on the MoS<sub>2</sub> surface in ionic-liquid gated devices, these fixed charges in the thin high- $\kappa$  dielectric layer could also reduce the Schottky barrier thickness, and thus contribute to the reported mobility enhancement. Also in carbon nanotube FETs, modest surface molecular doping has been shown to significantly reduce the Schottky barrier thickness, leading to a substantially enhanced tunneling current.[79]

To elucidate the transport mechanisms in the few-layer MoS<sub>2</sub> channel that was electrostatically doped by the ionic liquid, we measured the  $I_{ds}$ - $V_{bg}$  relationship in a different MoS<sub>2</sub> device (3.3 nm or 5 layers thick) between 77 and 180K, after the device had been quickly cooled from 250 K to 77 K at a fixed  $V_{ILg} = 0$  V. Below the freezing point of the ionic liquid ( $\approx 200$  K), the carrier charge density induced by the presence of positive ions, which preferentially enriched the vicinity of MoS<sub>2</sub>, remained practically constant. The carefully chosen value  $V_{ILg} = 0$  V of the ionic-liquid gate voltage allowed the creation of highly transparent tunneling contacts due to the adsorption of positive ions (implying *n*-doping), while the carrier density in the MoS<sub>2</sub> channel was kept low enough to allow an efficient reduction to zero by the back gate (see Fig. 3.5a). As shown in the inset of Fig. 3.5a, the  $I_{ds}$ - $V_{ds}$  characteristics are highly linear in the entire  $V_{ds}$  and  $V_{bg}$ -range even at 77 K, indicating highly transparent contacts with thin Schottky barriers. To confirm that it is the electrostatic surface doping that is responsible for the drastic reduction of the contact resistance, we compared the device characteristics before the

ionic liquid was added and after it was removed, following the completion of all electrical measurements. We observed nearly identical output characteristics in both cases (data not shown). Consequently, we may exclude the possibility of electrochemical doping or any other type of irreversible electrochemically induced degradation of the MoS<sub>2</sub> channel.

To avoid possible complications arising from the interplay between the ionic-liquid gate and the back gate, we performed  $I_{ds}$  - $V_{bg}$  measurements only at temperatures below the freezing temperature of the ionic liquid in order to suppress changes in the capacitance between the backgate and the MoS<sub>2</sub> channel. In our previous study of polymer-electrolyte-gated monolayer-thick  $MoS_2$  FETs, we attributed the beneficial influence of the polymer-electrolyte gate on the  $I_{ds}$ - $V_{bg}$ curves to a significant improvement of the carrier mobility.[80] However, the extent of mobility enhancement was overestimated by neglecting the additional ionic-liquid capacitance that was induced by the back-gate voltage. In addition, capacitive coupling between the back and top gates through the large top-gate bonding pad may also lead to a significant underestimate of the back-gate capacitance in conventional dual-gated FET devices, [62] thus causing a nominal overestimate of the mobility. Unlike in conventional top-gated (or dual-gated) devices, where the top-gate electrode is directly on top of the channel, inducing capacitive coupling, the metal gate electrode used in the ionic-liquid gate, shown in Fig. 3.1a, is located within the plane of the device and separated by several tens of micrometers, causing no change in the capacitance. As a result, the ionic-liquid gate electrode in our devices is capacitively decoupled from the transport channel and the back-gate in the temperature range between 77 and 180 K, ruling out the possibility of any stray capacitance arising from the gate electrode that may inadvertently cause a nominal increase in the back-gate capacitance. Our  $I_{ds}$ - $V_{bg}$  measurements with a floating and 36

grounded ionic-liquid gate, shown in Fig. 3.5a, yield identical results, indicating that the ionicliquid gate electrode has no effect on the back-gate capacitance when the ionic liquid is frozen.

**Figure 3.5.(a)** Transfer curves of a 3.3 nm thick (5 layer)  $MoS_2$  FET measured in the back-gate configuration with the drain-source bias  $V_{ds} = 100$  mV and the ionic-liquid-gate voltage kept at 0 V. The observations in the temperature range between 77 and 180 K were performed after the device had been cooled down from 250 to 77 K. The inset in(a) shows the output characteristics of the device measured at back-gate voltages between -60 and 60 V at T = 77 K. (b)

Temperature dependence of the field-effect mobility extracted from the transfer characteristics in (a). (c) Temperature dependence of the field-effect mobility of the same device before the ionic liquid was added.

Figures 3.5(b-c) show the temperature dependence of the low-field field-effect mobility extracted from the  $I_{ds}$ - $V_{bg}$  curves in Fig. 3.5a. These data are compared to the expected mobility in the same device with no ionic liquid present using the expression  $\mu = L/W \times dI_{ds}/dV_{bg}/(C_{bg}V_{ds})$ . For this estimate, we used  $L=4.5 \ \mu\text{m}$ ,  $W=0.7 \ \mu\text{m}$ , and  $C_{bg}=1.2 \times 10^{-8} \ \text{Fcm}^{-2}$  for the back-gate capacitance. The field-effect mobility with no ionic liquid present was observed to decrease from 5 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> to 0.3 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> as the temperature decreased from 295 K to 140 K, following a simple activation temperature dependence depicted in Fig. 5c. In this case, the mobility decreases much more rapidly than if it were limited by scattering from charged impurities.[81] This suggests that the charge transport behavior is largely limited by the Schottky barriers at the contacts and does not reflect the intrinsic behavior of the carrier mobility. We can extract an effective Schottky barrier height of  $\Phi \sim 66 \text{ meV}$  from the temperature dependence of the extrinsic mobility  $\mu \sim \exp(-\Phi/k_{\rm B}T)$  in Fig. 5c. This is lower than published theoretical estimates for an ideal interface,<sup>25</sup> possibly due to band bending induced by an applied gate voltage. In sharp contrast to this behavior, the mobility in presence of the ionic-liquid gate increases from ~100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> to ~ 220 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> as the temperature decreases from 180 K to 77 K at a carrier concentration between 7 × 10<sup>12</sup> and < 9 × 10<sup>12</sup> cm<sup>-2</sup> [determined from  $n_{2D} = C_{bg}(V_{bg} - V_{th})]$ , following a  $\mu \sim T^{\gamma}$  dependence with  $\gamma \approx 1$ . We conclude that in this case, the mobility is limited by the intrinsic behavior of the channel. Of course, dielectric screening in the ionic-liquid gate could nominally increase the capacitive coupling.[81] Still, the observed qualitative change from thermally activated to "metallic" behavior caused by an ionic liquid gate, which acts as a top

dielectric layer below the melting temperature, cannot be simply attributed to a possible underestimation of the back-gate capacitance. Extrapolating the  $\mu \sim T^{\gamma}$  fit with  $\gamma \approx 1$  to the temperature T=250 K yields a mobility value of  $\mu \approx 70$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, in good agreement with the mobility measured in the ionic liquid gate configuration at 250 K. This provides further evidence that the mobility measured in the back gate configuration is unlikely an artifact due to the underestimation of back gate capacitance. Moreover, as discussed in more detail below, our four-terminal measurements on a similar MoS<sub>2</sub> device show that the presence of the frozen ionic liquid, which forms an additional dielectric layer on top of the devices, does not substantially change the capacitance of the back-gate measurements.

Low-field field-effect channel mobility in this temperature range is affected by various scattering mechanisms, including scattering by acoustic phonons, optical phonons, as well as long range and short range disorder that is present both in the bulk and near the surfaces of the channel. Kaasbjerg*et al.* showed theoretically that the mobility due to acoustic and optical phonon scattering in monolayer MoS<sub>2</sub> increases with decreasing temperature following a  $\mu \sim T^{\gamma}$  dependence, where the exponent  $\gamma$  depends on the dominant scattering mechanism.[82] At relatively low temperatures ( < 100 K), acoustic phonon scattering dominates, resulting in  $\gamma = 1$ . At higher temperatures, optical phonon scattering starts to dominate, and the exponent  $\gamma > 1$  should cause a stronger temperature dependence of the mobility. On the other hand, the disorder-limited mobility decreases with decreasing temperature.[82, 83] In our few-layer devices, the observed exponent ( $\gamma \approx 1$ ) in the expression  $\mu \sim T^{\gamma}$  for the temperature dependence of the mobility coincides with that of transport dominated by acoustic-phonon scattering. In this case, however, the mobility values are substantially lower than what would be expected from acoustic-

phonon-limited mobility, and the temperature was high enough to excite not only acoustic, but also optical phonons. This behavior can be understood in a likely scenario, where the top ionic-liquid dielectric quenches phonon modes and thus reduces the  $\gamma$  value.